一生一芯F阶段学习笔记

本文最后更新于 2026年1月30日 凌晨

数字电路基础

基本门电路

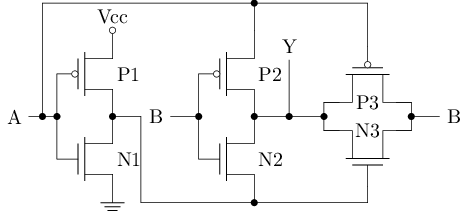

首先P/N结,带圈的低电压通,不带的高电压通。

异或门

异或的电路需要六个晶体管,主要原因是虽然四个就能完成真值表,但加上右边的P3/N3和B后,能保证

- 电平恢复

- 强驱动力

- 消除浮空节点

所以右边的部分是必要的

时序逻辑电路

D锁存器

为什么输入输出连接后会有Oscillation apparent?

因为

- 无稳定状态

- 信号传输有延迟

因此虽然输出会一直变化,但其实一个Oscillation apparent的状态

D触发器

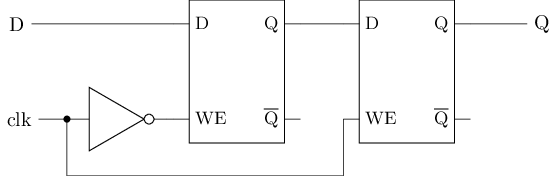

整体想法是我们如何控制一个锁存器只在clk上升时改变储存内容。

这里介绍的是主从式锁存器。

想法是使用一个非门创造一个条件使得主从锁存器无法同时写使能。

首先,低电平时,数据进入主锁存器。此时主读,从写不进

然后,变为高电平,形成上升端时,数据从主到从。此时主无法读,从能写能输出。

又因为此时无法读,所以主从锁存器的状态都不会改变,因此可以维持这个状态,不论输入怎么变化。

一生一芯F阶段学习笔记

https://chenxizhou233.github.io/posts/d075c4f3.html